The HyperX Difference

Next-Gen Processors for Life at the Edge™

The HyperX family was founded in 2005, after DARPA asked HyperX Logic to imagine what software-defined hardware might look like… and to build it.

In the early 2000s, edge computing only occurred in space and critical defense settings and that is where HyperX’s designs flourished, including deployment on the International Space Station.

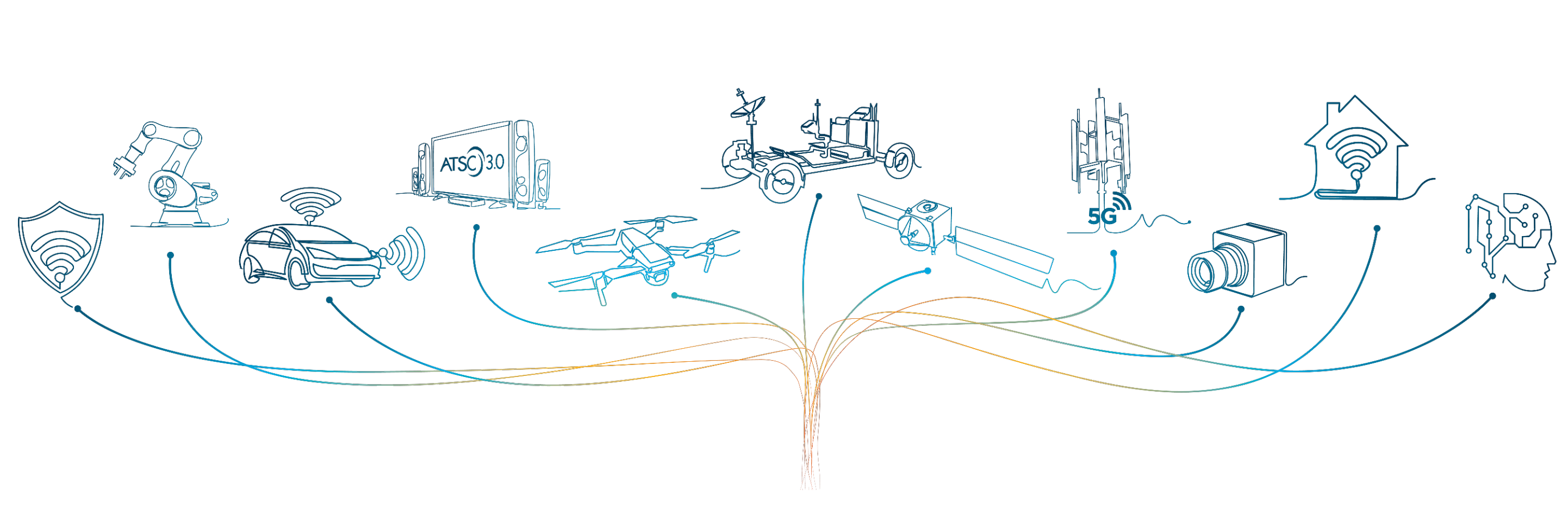

Today the Edge is everywhere, presenting the same requirements that HyperX was originally designed for:

- Real-time processing of wideband RF sources, cameras, and sensors

- Converged operations across dynamic response to multi-modal streaming inputs

- Edge decisioning; Intelligent response to changing environments

- Image, sound, voice and terrain recognition

- Compression, analysis and novel signal detection

After 20 years and nearly 400 patents later, HyperX is a leading C-programmable, low power, high-performance, software-defined System on Chip (SOC) perfect for Life at the Edge™.

20 years and nearly 400 patents later, HyperX is still the leader and the perfect solution for Life at the Edge™. Here’s why:

HyperX Accelerates Edge Convergence

Convergence is a central theme in every market. Space and terrestrial communications are converging. Multi-modal AI is convergence. Even consumer experiences are converging across media, next-gen television, and AR/VR devices.

HyperX accelerates convergence by enabling OEMs and ODMs to blur the lines themselves, both in development and in the field.

For starters, for every edge use case, there is a HyperX processor that is a perfect fit. All built around the same core concepts, all with exceptional performance, value, and best-in-class energy consumption.

HyperX development is highly efficient through a combination of hardware architecture and an abstracted development process, enabling faster development with less resource mapping complexity. HyperX Studio™ provides the tools needed to utilize C-programming, software debugging, modular reusable software, parallel development, cycle-accurate simulator, and the incredible time-to-market efficiency of using the same processor for design, development, and deployment..

In the field, HyperX shines again with wideband I/O, reprogrammability on the fly, <50ns task switching, ultra-low power consumption, and enough compute and wideband flexibility for significant in-field upgradeability.

Finally, HyperX reduces the time and cost of development by 75% compared to the leading FPGAs. That is a 4 to 1 development cycle advantage, or a 75% cost advantage, and you get to choose.

Winning at convergence requires speed to market, flexibility in-market, efficient development, and a low-cost BOM. HyperX ticks every box.

HyperX: The ECO - SYSTEM

Green computing matters. Analysts suggest that there will be 16.3 billion net new connected devices by 2030. That is unwelcome additional heat for planet Earth.

HyperX offers a way out. Our patented design only uses energy when it’s at work, and even then only enough for the task at hand. Moreover, our exceptional compute density, sub-50ns task switching and co-resident memory and processing elements mean that processes that used to take multiple chips or even multiple platforms can now be handled by a single HyperX processor.

Green computing at hyper-scale requires five distinct capabilities, all achieved by HyperX through our patented design:

- Exceptional compute and I/O density

- Ultra-low power consumption

- C-programmability and the most advanced embedded development environment

- Best price/value

- The ability to design, develop and go-to-market on the same processor

HyperX Advantages:

Performance:

- On-chip wideband memory-network fabric

- A massive array of Processing Elements (PEs)

- Parallel processing of operations across PEs and Data and Memory Routers

- Multiple processor operations per clock cycle

- <50ns program switching

- Instantaneous bandwidth on demand

Efficiency:

- Dynamic power utilization cycle-to-cycle

- Up to 50% less power per chip compared to leading FPGAs

- Normally operates at 80-90% utilization

- Essentially no power used by inactive processing elements

- Ultra-low heat generation

Programability:

- C-programmable with robust HyperX Studio tools

- Rapid code, build, test, and optimize iterative development

- Standard software debugging tools

- Parallel development across developers

- Modular reusable software across designs

- 75% faster time-to-market vs. ASICs and FPGAs

Price / Value:

- Family of software-definable processors for every scale: sensor to supercomputer

- Exceptional compute power at every process node

- Common architecture, common programming across the family

- Reprogrammable on the fly for in-field future proofing.

- Design, prove and go-to-market with the same processor

Moore’s Wall: Rescheduled for 2050 (but just for us…)

HyperX technology significantly outperforms its competitors. A seven-nanometer processor from HyperX Logic can outperform a three-nanometer processor from a competitor. That gives us about four additional generations before we become affected by Moore’s wall, or 20-25 years we can push Moore’s Wall back. An investment in working with HyperX pays dividends long into the future.

Whitepaper on how we avoid Moore’s wall

Create with HyperX Studio™

HyperX was built by developers, for developers, and it shows in the robust set of tools we provide for every customer:

- HyperX ISDE™

- Development libraries

- Cycle accurate simulation

- Hardware layout editor

- Performance and power measurement tools

- Software-defined processor operations

- Standard software development debugging tools

- Development boards

- Developer community and robust support options